便利なDDS IC AD9833

このところDDSを扱う事が増えております.今取り組んでいるのはFPGAで作る特殊なDDSです.でも普段は汎用のAD社のAD9833をよく使っています.AD9833の仕様は,位相アキュムレータ28ビット,最高クロック25MHz,DAC 10Bit,出力0.65Vです.ちなみに25MHzクロックと28Bitアキュムレータから計算される周波数分解能は0.0931Hzになります.

AD9833は3本のシリアル通信でマイコンとつながるのでハードは極めてすっきりします.このシリアルのクロックレートは最高40MHzが可能で,高速のDSPやFPGAで駆動すれば本格的なFM変調も簡単にかける事ができます.さらにAD9833には周波数レジスタのほかに12ビット分解能の位相レジスタもあるので,2台以上を同期で使えば高精度なIQ信号や三相交流も簡単に作れます.

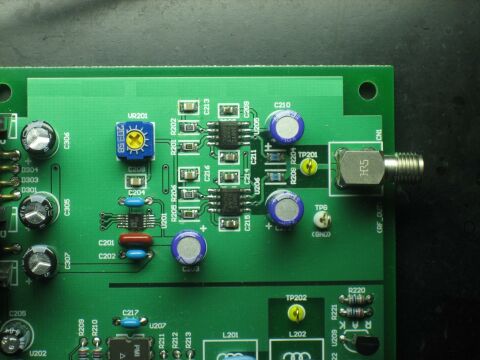

AD9833の後にはLPFを入れOPアンプで増幅します.私の定番OPアンプはTI社のTHS3001です.このTHS3001は420MHzの帯域幅と6500V/μsecのスルーレート,そして高速にも係らず±15Vの電源で使う事ができます.さらに電流が100mAも取れるのでパラ運転すれば50Ω系の負荷も楽々駆動します.

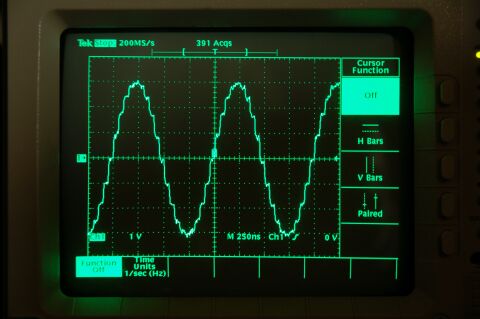

クロック20MHzでAD9833を動かした時の波形が下記です.左は1KHz出力時の波形で大変奇麗です.右は1MHz時の波形です.1MHzでは飛び飛びにサイン波データを参照するので階段波形になります.さらに10MHzでは完全に方形波になりました.そのままの出力で綺麗な波形を得たいなら100kHzまで,サンプリング定理を考慮したフィルタをガッツリ入れて使うなら5MHzまででしょうか.

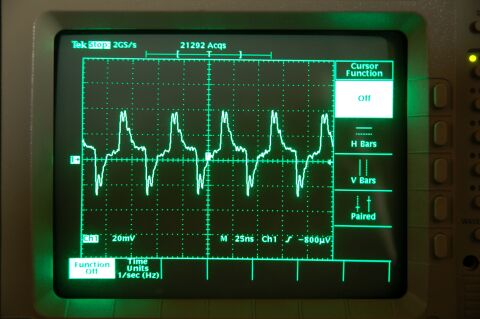

次の写真は0Hz出力時の波形です.20倍のアンプを通しているので80mVp-pのノイズが見られます.AD9833の出力レベルに換算しても4mVp-p.DAの出力0.65Vを10Bit解像度で考えると1LSBは0.65mVなので,やはり大きいと言えます.このAD9833で唯一感じる困り事はこのノイズなのです.そしてこれはデータシートには載っていません.でもこのノイズはAD9833の直後にLCフィルタを設ける事で簡単に除去することが出来ます.