パルスジェネレータの出力アンプ3

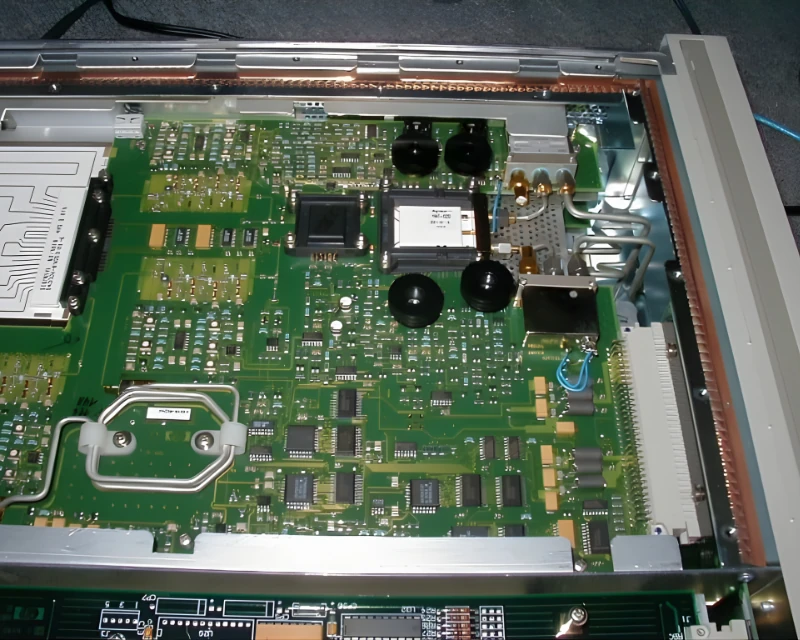

HP8133Aという3GHzの超高速パルスジェネレータがあります(写真1)。パルス幅は最小150psを出力し1ps刻みで幅を変えられます。これを30年ほど前ECLの超高速デジタル回路で使用しました。HP8133Aに加えて当時としては最新の8GHzオシロとのレンタル。月の支払いが200万近くだったのを覚えています。GHzにも及ぶロジック回路は当時ECLで組むのが当たり前でした。GHzというと難しそうですが基本を押さえていれば設計は簡単です。なぜならECLはリニア動作だからです。むしろ74ACの方がチャタリングがあり苦労します。

このHP8133Aはいったいどんな回路で超高速を実現しているのか。エンジニアとしてとても興味はあるのですがレンタル品なので中は空けられません。それから20年ほどたってなんとか中古品を手に入れることができました。さっそく中を観察。さぞや凄いトリッキーな回路のオンパレードかと思っていたのですが、意外にも教科書的な回路が整然と並んでいる。唯一違うのは半導体の性能です。日本には紹介されていない海外製の超高速ICの数々。

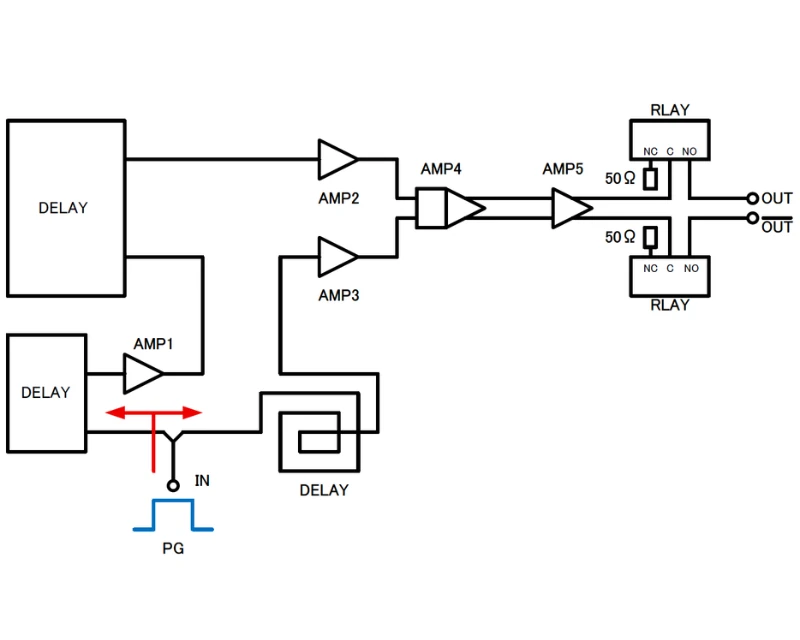

構成はおよそ図1の様になっていました。元となるパルスは二手に分かれ、一方は可変遅延回路を通ってその後XORで再び合流。さらにアンバランスからバランスに変換されて最後は出力アンプで出力。

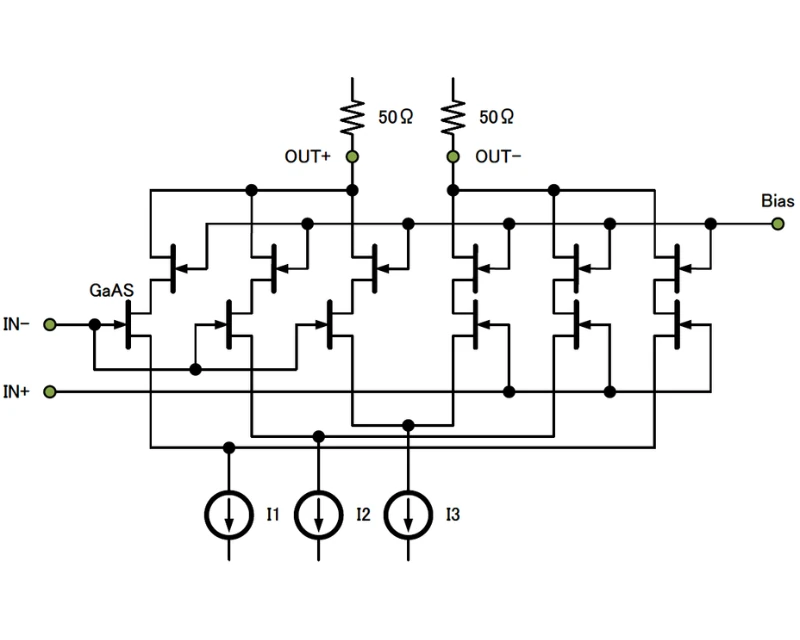

この出力アンプですがHPのオリジナルのハイブリッドICで、別資料によるとGaAS_FETによるカスコード差動アンプです。図2の様にアンプは3アームのパラレルで各アーム毎に電流が変えられるようになっています。そしてFETの電流出力を50Ωでノートン・テブナン変換して出力していました。